#### Interscience Research Network

#### Interscience Research Network

Conference Proceedings - Full Volumes

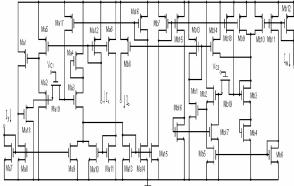

**IRNet Conference Proceedings**

9-22-2012

## Proceedings of International Conference on Electrical, Electronics & Computer Science

Prof.Srikanta Patnaik Mentor IRNet India, patnaik\_srikanta@yahoo.co.in

Follow this and additional works at: https://www.interscience.in/conf\_proc\_volumes

Part of the Computer Engineering Commons, and the Electrical and Electronics Commons

#### **Recommended Citation**

Patnaik, Prof.Srikanta Mentor, "Proceedings of International Conference on Electrical, Electronics & Computer Science" (2012). Conference Proceedings - Full Volumes. 46. https://www.interscience.in/conf\_proc\_volumes/46

This Book is brought to you for free and open access by the IRNet Conference Proceedings at Interscience Research Network. It has been accepted for inclusion in Conference Proceedings - Full Volumes by an authorized administrator of Interscience Research Network. For more information, please contact sritampatnaik@gmail.com.

## Proceedings of International Conference on

## **ELECTRICAL, ELECTRONICS & COMPUTER SCIENCE**

Interscience Research Network (IRNet)

Bhubaneswar, India

#### **Editorial**

In the era of telephones very few had predicted its wide impact on mankind. Initially from the bulky telephone sets gradually moving on towards smaller and more sophisticated handy versions, the telecommunication system has come a long way. The birth of cellular phones, popularly referred to as cell phones or mobile phones created endless possibilities in the field of communication. The cell phones which were used till the early 90's were mere wireless hand set phones for verbal communications. But in the late 90's and during the dawn of 21st. century brought the paradigm to a new level. The cell phones were now developed not only for the purpose of making calls but also for a range of other purposes. The term 'Smartphone' came into existence in true sense only after the launch of the revolutionary product form Apple, called the 'iPhone' (2007) which changed the way people looked at mobile phone. It is no longer a medium for communication rather an important part of life and the Smartphone market has never again looked back ever since. In just 5 years the Smartphone became, from a mere Electronics device to a bare necessity.

The Smartphones today already possess a wide range of features ranging from providing high internet access to health monitoring. They have now become a one stop solution for all problems. Today the controller of an organization can keep a track of what is happening in his office even, he is miles away. Even a layman can easily learn to operate the smartphones in a few hours as it is very user-friendly. Now this tremendous improvement is something that has taken place in a time span of 5 years. Imagine what would happen in another say 5 years, or 10 years, or say 100 years? Where will this technology drive the mankind to? In the future, they may evolve into personal mobile computers. Assuming that Moore's law holds true, mobile CPUs with near supercomputing speeds will be entirely possible. The number, accuracy and performance of sensors will grow, the combination of which will give the users a very powerful sense of the surroundings.

It might even take place of a wrist watch which would make use of peripherals, like information glasses and headsets, not only these peripherals allow the user to explicitly interact with the digital and physical word, but they'll also provide subtle cues to users subconscious. As a developer, engineer and product designer one might be working on something beyond expectations. Who knows, what the future will give the society but one can at least be sure of one thing, that is, the current technologies will shape the future. Therefore it is rightly said

"Inventor: A person who makes an ingenious arrangement

of wheels, levers and springs, and believes it's civilization." Ambrose Bierce

So this conference has been designed to stimulate the young minds including Research Scholars, Academicians, and Practitioners to contribute their ideas, thoughts and nobility in these disciplines of engineering. It is pleasure to welcome all the participants, delegates and organizer to this international conference on behalf IOAJ family members. IOAJ has received a great response from all parts of country and abroad for the presentation and publication in the proceeding of the conference.

I sincerely thank all the authors for their valuable contribution to this conference. I am indebted towards the reviewers and Board of Editors for their generous gifts of time, energy and effort.

Editor-in-Chief

Dr. Srikanta Patnaik

## A HIGH PERFORMANCE PARALLEL DISTRIBUTED ARITHMETIC DCT ARCHITECTURE

#### <sup>1</sup>SOLA RANJITH HARITHA, <sup>2</sup>NAGANABOINA, <sup>3</sup>RANGU SRIKANTH & <sup>4</sup>BILLA RANJITH KUMAR

<sup>1,2</sup>M. Tech scholar, Ganapathy Engineering College <sup>1</sup>ECE Department, <sup>2</sup>M.Tech scholar, <sup>1,2</sup>Jayamukhi Institute of Technological Sciences

**Abstract**— In this brief, by operating the shifting and addition in parallel, an error-compensated adder-tree (ECAT) is proposed to deal with the truncation errors and to achieve low-error and high-throughput discrete cosine transform (DCT) design. Instead of the 12 bits used in previous works, 9-bit distributed arithmetic-precision is chosen for this work so as to meet peak-signal-to-noise-ratio (PSNR) requirements. Thus, an area-ef-ficient DCT core is implemented to achieve 1 Gpels/s throughput rate with gate counts of 22.2 K for the PSNR requirements outlined in the previous works.

Keywords -Distributed arithmetic (DA)-based, error-compensated adder-tree (ECAT), 2-D discrete cosine transform (DCT).

#### I. INTRODUCTION

Discrete cosine transform (DCT) is a widely used tool in image and video compression applications. Recently, the high-throughput DCT designs have been adopted to fit the requirements of real-time applications.

To reduce area, ROM-based distributed arithmetic (DA) was applied in DCTcores .Uramotoetal implemented the DA-based multipliers using ROMs to produce partial products together with adders that accumulated these partial products. In this way, instead of multipliers, the DA-based ROM can be applied in a DCT core design to reduce the area required. In addition, the symmetrical properties of the DCT transform and parallel DA architecture can be used in reducing the ROM size. Shams et al. employed a bit-level sharing scheme to construct the adder-based butterfly matrix called new DA (NEDA)]. Being compressed, the butterfly-addermatrix in utilized 35 adders and 8 shift-addition elements to replace the ROM. Based on NEDA architecture, the recursive form and arithmetic logic unit (ALU) were applied in DCT design to reduce area cost. Hence the NEDA architecture is the smallest architecture for DA-based DCT core designs, but speed limitations exist in the operations of serial shifting and addition after the DAcomputation. The high-throughput shift-adder-tree (SAT) and adder-tree (AT), those unroll the number of shifting and addition words in parallel for DAbased computation. However, a large truncation error occurred. In order to reduce the truncation error effect, several error compensation bias methods have been presented based on statistical analysis of the relationship between partial products and multipliermultiplicand. However, the elements of the truncation part outlined in this work are independent so that the

previously described compensation methods cannot be applied.

This brief addresses a DA-based DCT core with an error-compensated adder-tree (ECAT). The proposed ECAT operates shifting and addition in parallel by unrolling all the words required to be computed. Furthermore, the error-compensated circuit alleviates the truncation error for high accuracy design. Based on low-error ECAT, the DA-precision in this work is chosen to be 9 bits instead of the traditional 12 bits so as to achieve the peak-signal-to-noise-ratio (PSNR) requirements. Therefore, the hardware cost is reduced, and the speed is improved using the proposed ECAT.

This brief is organized as follows. In Section II, the mathematical derivation of the distributed arithmetic is given. The proposed ECAT architecture is discussed in Section III. The proposed 8 8 2-D DCT core is demonstrated in Section IV. The comparisons and results are presented in Section V, and conclusions are drawn in Section VI.

### II. MATHEMATIAL DERIVATION OF DISTRIBUTED ARITHMETIC

The inner product is an important tool in digital signal processing applications. It can be written as follows:

$$Y = AX = \sum_{i=1}^{L} AX_i \tag{1}$$

Whee Ai, Xi, and L are with fixed coefficient, with input data, and number of inputs, respectively. Assume that coefficient  $A_i$  is Q-bit two's complement binary fraction number. Equation (1) can be expressed as follows:

$$Y = \begin{bmatrix} 2^{0} & 2^{-1} & \dots & 2^{-(Q-1)} \end{bmatrix}$$

$$\begin{bmatrix} A_{1,0} & A_{2,0} & \cdots & A_{L,0} \\ A_{1,1} & A_{2,1} & \cdots & A_{L,1} \\ \vdots & \vdots & \ddots & \vdots \\ A_{1,(Q-1)} & A_{2,(Q-1)} & \cdots & A_{L,(Q-1)} \end{bmatrix} \begin{bmatrix} X_{1} \\ X_{2} \\ \vdots \\ X_{L} \end{bmatrix}$$

$$= \begin{bmatrix} 2^{n} & 2^{-1} & \cdots & 2^{-(Q-1)} \end{bmatrix} \begin{bmatrix} y_{0} \\ y_{1} \\ \vdots \\ y_{(Q-1)} \end{bmatrix}$$

$$(2)$$

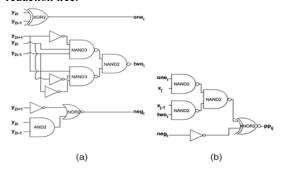

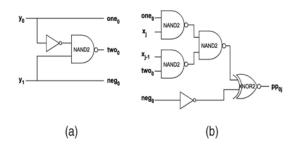

Where  $y_j = \sum_{i=1}^{L} A_{i,j} X_{i,j} A_{i,j} \in \{0,1\}$  for  $1 \le j \le (Q-1)$ , and  $A_{j,j} \in \{-1,0\}$  for j = 0, Note that  $y_0$  may be 0 or a negative number due to two's complement representation. In (2),  $y_i$  values. Thus the inner product computation in (1) can Fig.1. Q-Pbit words shifting and addition operations is parallel. be implemented by using shifting and adders instead of multipliers. Therefore, low hardware cost can be achieved by sing DA-based architecture.

#### III. **ECAT ARCHITECTURE**

From (2), the shifting and addition computation can be written as follows:

$$Y = \sum_{j=0}^{Q-1} y_j, 2^{-1}$$

(3)

In general, the shifting and addition computation uses a shift-and-add operator in VLSI implementation in order to reduce hardware cost. However, when the number of the shifting and addition words increases. the computation time will also increase. Therefore, the shift-adder-tree (SAT) presented in operates shifting and addition in parallel by unrolling all the words needed to be computed for high-speed applications. However, a large truncation error occurs in SAT, and an ECAT architecture is proposed in this brief to compensate for the truncation error in highspeed applications.

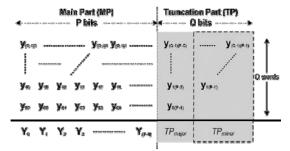

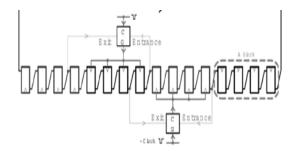

In Fig. 1, the Q P-bit words operate the shifting and addition in parallel by unrolling all computations. Furthermore, the operation in Fig. 1 can be divided into two parts: the main part (MP) that includes most significant bits (MSBs) and the truncation part (TP) that has least significant bits (LSBs). Then, the shifting and addition output can be expressed as follows:

$$Y = M P + T P2^{-(P-2)}$$

(4)

The output Y will obtain the P-bit MSBs using a rounding operation called post truncation (Post-T), which is used for high-accuracy applications. However, hardware cost increases in the VLSI design. In general, the TP is usually truncated to reduce hardware costs in parallel shifting and addition operations, known as the direct truncation (Direct-T) method. Thus, a large truncation error occurs due to the neglecting of carry propagation from the TP to MP. In order to alleviate the truncation error effect, several error compensation bias methods have been presented]. All previous works were only applied in the design of a fixedwidth multiplier. Because the products in a multiplier have a relationship between the input multiplier and multiplicand, the compensation methods usually use the correlation of inputs to calculate a fixed or an adaptive compensation bias using simulation or statistical analysis. Note that the addition elements in the TP in Fig. 1 (where  $1 \le q \le (Q-1)$  and (P-q-1) $\leq p \leq (P-1)$  are independent from each other. Therefore, the previous compensation method cannot be applied in this work, and the proposed ECAT is explained as follows.

#### A. Proposed Error-Compensated Scheme

From Fig.1, (4) can be approximated as  $Y \approx MP + \sigma \cdot 2^{-(P-2)}$ (5)

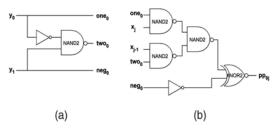

Fig.2 Proposed ECAT architecutre of shifting and addition operators for the (P, Q) = (1, 26) example.

Where  $\sigma$  is the compensated bias from the TP to the MP as listed in (6)–(8)

$$\sigma = \text{Round} \left( \text{TP}_{\text{major}} + \text{TP}_{\text{minor}} \right) \tag{6}$$

$$TP_{\text{minor}} = \frac{1}{2} \sum_{j=0}^{Q-1} y_{j(P-1-j)}$$

$$TP_{\text{minor}} = \frac{1}{4} \left( y_{1(P-1)+...+y(Q-1)(P-Q+1)} \right)$$

$$+ \frac{1}{8} \left( y_{2(P-1)+...+y(Q-1)(P-Q+2)} \right)$$

$$+ \left( \frac{1}{2} \right)^{Q} y_{(Q-1)(P-1)}$$

(8)

Where Round() is rounded to the nearest inter. The has more weight than TP<sub>minor</sub> when contributing towards the Therefore, the compensated bias  $\sigma$  can be calculated by obtaining  $TP_{major}$  and estimating  $TP_{minor}$ . Let the probability of  $y_{qp}=1$  be 0.5, where  $1\leq q\leq (Q-1)$  and  $(P-q-1)\leq (P-1)$ . Hence, (8) can be expressed as follows:

TP<sub>minor</sub> =

$$\frac{1}{4} \left( \frac{1}{2} (Q - 1) \right) + \dots + \left( \frac{1}{2} \right)^{Q+1}$$

=  $\left( \frac{1}{2} \right)^{Q+2} \sum_{n=1}^{Q-1} n \cdot 2^n = \frac{(Q-2)}{4} + \left( \frac{1}{2} \right)^{Q+1}$ . (9)

For a given  $\operatorname{TP}_{\operatorname{major}}$ ,  $(y_{j(p-1-j)}, 0 \le j \le (Q-1))$ , the  $\sigma$  can be obtained after rounding the sum of  $(\operatorname{TP}_{\operatorname{major}} + \operatorname{TP}_{\operatorname{minor}})$ . In order to round the summation,

$\ensuremath{\text{TP}_{\text{minor}}}$  can be divided into four parts:

$$TP_{\text{minor}} = \begin{cases} k - \frac{1}{2} + \left(\frac{1}{2}\right)^{4k+1}, & \text{for } Q = 4k \\ k - \frac{1}{4} + \left(\frac{1}{2}\right)^{4k+2}, & \text{for } Q = 4k+1 \\ k + \left(\frac{1}{2}\right)^{4k+3}, & \text{for } Q = 4k+2 \\ k + \frac{1}{4} + \left(\frac{1}{2}\right)^{4k+4}, & \text{for } Q = 4k+3. \end{cases}$$

$$(10)$$

As  $k \ge 1$ , the TP<sub>minor</sub> approximates (11)

$$\text{TP}_{\text{minor}} \approx \begin{cases} (k-1) + \frac{1}{2}, & \text{for } Q = 4k \\ (k-1) + \frac{3}{4}, & \text{for } Q = 4k + 1 \\ k, & \text{for } Q = 4k + 2 \\ k + \frac{1}{4}, & \text{for } Q = 4k + 3. \end{cases}$$

(11)

Hence,  $\sigma$  can be rewritten as three cases.

Case 1)

$$Q = 0, 1, 2, 3$$

$\sigma = \text{Round (TP}_{\text{major}}),$

Case 2)  $Q = 4k, 4k + 1(k \ge 1)$

$\sigma = (k-1) + \text{Round (TP}_{\text{major}} + 0.5),$  (13)

TABLE I

COMPARISONS OF ABSOLUTE AVERAGE ERROR

, MAXIMUM

| Error                  | (P, Q)   | (12, 3) | (12, 6) | (12, 9) | (12, |

|------------------------|----------|---------|---------|---------|------|

|                        |          | case1   | case3   | case2   | 12)  |

|                        | Direct-T | 1.0625  | 2.5078  | 4.0010  | 5.50 |

|                        |          |         |         |         | 01   |

| 3                      | Proposed | 0.2656  | 0.3789  | 0.3804  | 0.47 |

| C                      |          |         |         |         | 38   |

|                        | Post-T   | 0.2500  | 0.2500  | 0.2500  | 0.25 |

|                        |          |         |         |         | 00   |

|                        | Direct-T | 2.1250  | 5.0156  | 8.0020  | 11.0 |

|                        |          |         |         |         | 00   |

|                        | Proposed | 0.6250  | 1.5000  | 2.0020  | 3.00 |

| $\varepsilon_{ m max}$ |          |         |         |         | 00   |

|                        | Post-T   | 0.5000  | 0.5000  | 0.5000  | 0.50 |

|                        |          |         |         |         | 00   |

|                        | Direct-T | 1.3516  | 6.7614  | 16.730  | 31.2 |

| 3                      |          |         |         |         | 24   |

| Proposed | 0.1016 | 0.2184 | 0.2222 | 0.34 |

|----------|--------|--------|--------|------|

| _        |        |        |        | 72   |

| Post-T   | 0.0859 | 0.0834 | 0.0833 | 0.08 |

|          |        |        |        | 33   |

Case 3)

$$Q = 4k + 2, 4k + 3(k \ge 1)$$

$\sigma = k + \text{Round}(TP_{\text{major}}),$  (14)

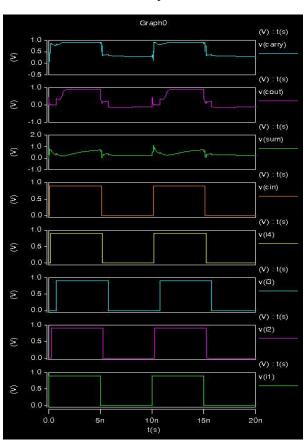

#### B. Performance Simulation for an Error-Compensated Circuit

In this subsection, comparisons of the absolute average error  $\varepsilon$ , the maximum error  $\varepsilon_{max}$ , and the mean square error  $\varepsilon_{max}$ , for the proposed error=compensated circuit with Direct-T and Post-T are listed in Table I.

The  $\varepsilon$ ,  $\in_{\text{max}}$ , and  $\in_{\text{max}}$ , are defined as follows:

$$\in = Avg[TP - \sigma]$$

(15)

$$\varepsilon_{\text{max}} = \text{m a } \{ \text{TP} = \sigma | \}$$

(16)

$$\varepsilon_{\text{max}} = Avg\left\{ (\text{TP} = \sigma)^2 \right\}$$

(17)

Where  $Avg\{\}$  is the average operator.

The internal word-length usually uses 12 bits in a DCT design. Consequently, word length P=12 is chosen together with different values of 3, 6, 9, and 12, which are listed in Table I. The Post-T method provides the most accurate values for fixed-width computation nowadays. In addition, the Direct-T method has the largest inaccuracies of the errors shown in Table I for low-cost hardware design. The proposed ECAT is more accurate than Direct-T and is close to the performance of the Post-T method using a compensated circuit. Because the truncation part  $TP_{minor}$  is estimated using statistical analysis, the magnitude of errors also increases as the number of shift-and-add words Q increases.

#### C. Proposed ECAT Architecture

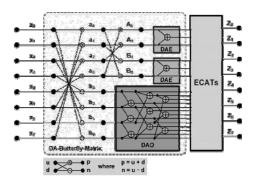

The proposed ECAT architecture is illustrated in Fig. 2 for (P, Q) = (12,6) ((case 3), where block FA indicates a full-adder cell with three inputs (a, b, and c) and two outputs, a sum (s) and a carry-out (co). Also, block HA indicates half-

TABLE II COMPARISONS OF ABSOLUTE AVERAGE ERROR  $\in$ , MAXIMUM ABSOLUTE ERROR  $\in$ <sub>max</sub>, AND MEAN

SOUARE ERROR €....

|                      |            | mse    |          |

|----------------------|------------|--------|----------|

|                      | Shift-and- | SAT    | Proposed |

|                      | add        |        | ECAT     |

| Area                 | 236        | 406    | 463      |

| (gates)              |            |        |          |

| Delay (ns)           | 10.8       | 3.72   | 3.89     |

|                      |            |        |          |

| Area                 | 100 %      | 59.3 % | 70.7 %   |

| × delay              |            |        |          |

| $\in_{\mathit{mse}}$ | 0.326      | 6.761  | 0.218    |

|                      |            |        |          |

adder cell with two inputs (a and b) and two outputs, a sum (s) and a carry-out(co). The comparisons of area, delay, area-delay product, and accuracy for the proposed ECAT with other architectures are listed in Table II. The area and delay are synthesized using a Synopsys Design Compiler with the Artisan TSMC 0.18-  $\mu$ m Standard cell library.

The proposed ECAT has the highest accuracy with a moderate area-delay product. The shift-and-add method has the smallest area, but the overall computation time is equal to  $10.8(=1.8\times6)$  ns that is the longest. Similarly, the SAT, which truncates the TP and computes in parallel, takes 3.72 ns to complete the computation and uses 406 gates, which is the best area-delay product performance. However, for system accuracy, the SAT is the worst option shown in Table II. Therefore, the ECAT is suitable for high-speed and low-error applications.

#### IV. PROPOSED 8 2 D DCT CORE DESIGN

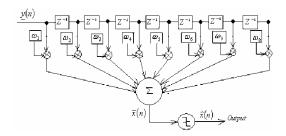

The 1-D DCT employs the DA-based architecture and the proposed ECAT to achieve a high-speed, small area, and low- error design. The 1-D 8-point DCT can be expressed as follows:

$$Z_{n} \frac{1}{2} k_{n} \sum_{m=0}^{7} x_{m} \times \cos\left(\frac{(2m+1)n\pi}{16}\right)$$

(18)

Where  $x_m$  denotes the input data;  $Z_n$  denotes the transform output;

$0 \le n \le 7$ ;  $k_n = 1/\sqrt{2}$  for n = 0; and  $k_n = 1$  for other n values. By neglecting the scaling factor 1/2, the 1-D 8-point DCT in (18 can be divided into even and odd parts:  $\mathbf{Z}_e$  and  $\mathbf{Z}_o$  as listed in (19) and (20), respectively.

$$\mathbf{Z}_{o} = \begin{bmatrix} Z_{0} \\ Z_{2} \\ Z_{4} \\ Z_{6} \end{bmatrix} = \begin{bmatrix} c_{4} & c_{4} & c_{4} & c_{4} \\ c_{2} & c_{6} & -c_{6} & -c_{2} \\ c_{4} & -c_{4} & -c_{4} & c_{4} \\ c_{6} & -c_{2} & c_{2} & -c_{6} \end{bmatrix} \begin{bmatrix} a_{0} \\ a_{1} \\ a_{2} \\ a_{3} \end{bmatrix} = \mathbf{C}_{e} \cdot \mathbf{a} \quad (15)$$

$$\mathbf{Z}_{o} = \begin{bmatrix} Z_{1} \\ Z_{3} \\ Z_{5} \\ Z_{5} \end{bmatrix} = \begin{bmatrix} c_{1} & c_{3} & c_{5} & c_{7} \\ c_{3} & -c_{7} & -c_{7} & -c_{5} \\ c_{5} & -c_{1} & c_{7} & c_{3} \\ c_{7} & -c_{8} & c_{7} & -c_{7} \end{bmatrix} \begin{bmatrix} b_{0} \\ b_{1} \\ b_{2} \\ b_{3} \end{bmatrix} = \mathbf{C}_{e} \cdot \mathbf{b} \quad (20)$$

Where  $c_i = \cos(i\pi/16)$ . Moreover, the even part  $\mathbf{Z}_e$  can be further decomposed into even and odd parts:  $\mathbf{Z}_{ee}$  and  $\mathbf{Z}_{eo}$

$$\mathbf{Z}_{e \in} = \begin{bmatrix} Z_0 \\ Z_4 \end{bmatrix} = \begin{bmatrix} c_4 & c_4 \\ c_4 & -c_4 \end{bmatrix} \begin{bmatrix} A_0 \\ A \end{bmatrix} = \mathbf{C}_{ee} \cdot \mathbf{A} \qquad (21)$$

$$\mathbf{Z}_{eo} = \begin{bmatrix} Z_2 \\ Z_6 \end{bmatrix} = \begin{bmatrix} c_2 & c_6 \\ c_6 & -c_2 \end{bmatrix} \begin{bmatrix} B_0 \\ B_1 \end{bmatrix} = \mathbf{C}_{eo} \cdot \mathbf{B} \qquad (22)$$

For the DA-based computation, the coefficient matrix  $\mathbf{C}_o$ ,  $\mathbf{C}_{ee}$ , and  $\mathbf{C}_{e0}$ , are expressed as 9-bit binary fraction numbers. Table III expresses  $\mathbf{Z}_{ee}$  ( $Z_0$  and  $Z_4$ ) in the bit level formulation. In Table III, using given input data  $A_0$  and  $A_1$ , the

TABLE III 9-BIT DA-BASED COEFFICIENT MATRIX  $\mathbf{C}_{ee}$

| 2      | $Z_0$       |        | $Z_4$       |

|--------|-------------|--------|-------------|

| Weight | Value       | Weight | Value       |

| -2°    | 0           | -2°    | $A_1$       |

| 2-1    | $A_0 + A_1$ | 2-1    | $A_0$       |

| 2-2    | 0           | 2-2    | $A_{l}$     |

| 2-3    | $A_0 + A_1$ | 2-3    | $A_0$       |

| 2-4    | $A_0 + A_1$ | 2-4    | $A_0$       |

| 2-5    | 0           | 2-5    | $A_{l}$     |

| 2-6    | $A_0 + A_1$ | 2-6    | $A_0$       |

| 2-7    | 0           | 2-7    | $A_1$       |

| 2-8    | $A_0 + A_1$ | 2-8    | $A_0 + A_1$ |

transform output  $\mathbf{Z}_{ee}$  needs only one adder to compute  $(A_0 + A_1)$  and two separated ECATs to o b t a i n t h e r e s u l t s o f  $Z_0$  and  $Z_4$ . Similarly, the other transform outputs  $\mathbf{Z}_{eo}$  and  $\mathbf{Z}_o$  can be implemented in DA-based forms using 10(=1+9)

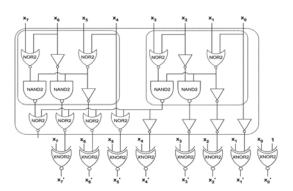

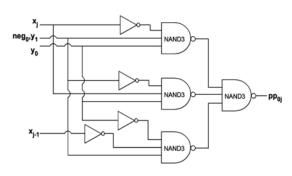

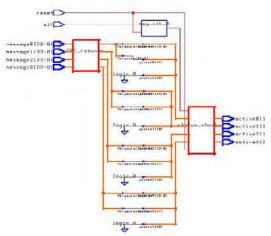

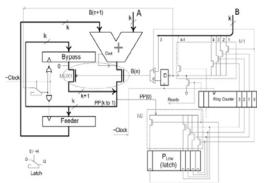

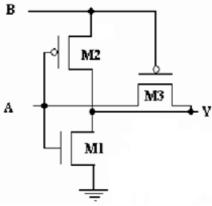

adders and corresponding ECATs. Consequently, from the (19)–(22), the proposed 1-D 8-point DCT architecture can be constructed as illustrated in Fig. 3 using a DA-Butterfly-Matrix, that includes two DA even processing elements (DAEs), a DA odd processing element (DAO) and 12 adders/subtractors, and 8 ECATs (one ECAT for each transform output). The eight separated ECATs work simultaneously, enabling high-speed applications to be achieved. After the data output from the DA-Butterfly-Matrix is completed, the transform output  ${\bf Z}$  will be completed during one clock cycle by the proposed ECATs. In contrast, the traditional shift-and-add architecture requires  ${\cal Q}$  clock cycles to complete the transform  ${\bf Z}$  output if the DA-precision is  ${\cal Q}$  bits.

With high-speed considerations in mind, the proposed 2-D DCT is designed using two 1-D DCT cores and one transpose buffer. For accuracy, the DA-precision and transpose buffer word lengths are chosen to be 9 bits and 12 bits, respectively, meaning that the system can meet the PSNR requirements

outlined in previous works. Moreover, the 2-D DCT core accepts 9-bit image input and 12-bit output precision.

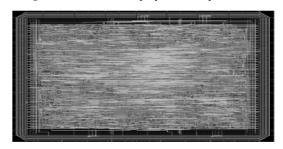

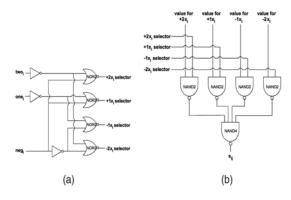

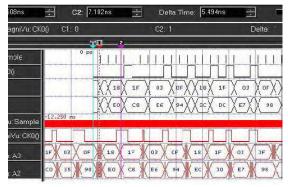

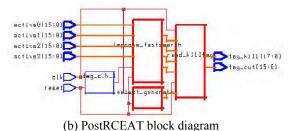

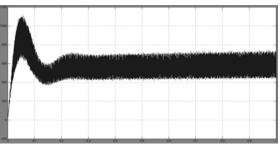

For the proposed 2-D DCT, the Synopsys Design Compiler was applied to synthesize the RTL design of the proposed core, and the Cadence SoC Encounter was adopted for placement and routing (P&R). Implemented in a 1.8-V TSMC 0.18-µm 1P6M CMOS process, the proposed 8 × 8 2-D DCT core has a latency of 10 clock cycles and is operated at 125 MHz. As a result of the 8 parallel outputs, the proposed 2-D DCT core can achieve a throughput rate of 1 Gpixels per second (= 8 × 125 MHz), meeting the 1080 p (1920 × 1080 × 60 pixels/s) high definition television (HDTV) specifications for 200 MHz based on low power operations. The core layout and simulated characteristics are shown in Fig. 4.

Table IV compares the proposed 8 × 8 2-D DCT core with previous 2-D DCT cores. In [3], a multiplier-based DCT core based on pipeline radix-42 single delay feedback path (R42 SDF) architecture to achieve high-speed design. The ROM-based DCT core is presented to reduce hardware cost. A NEDA architecture is presented by using adders to reduce the chip area of DCT core. Nevertheless, a speed limitation for shift-and-add is in NEDA design. The SAT and AT architectures for DA-based DCTs improve the throughput rate of the NEDA method. However, DA-precision must be chosen as 13 bits to meet the system.

|                                             | Line et al. [3]  | Uramoto et al.[4] | Shame et al. [7]  | Chungam et al. [10] | Huang et al. [11] | Proposed    |

|---------------------------------------------|------------------|-------------------|-------------------|---------------------|-------------------|-------------|

| Architecture                                | Multiplier-based | ROM-based         | NEDA              | DA-based            | DA-based          | DA-based    |

| Technology                                  | 0.13µmm          | 0.8µm             | 0. <b>1</b> 8µm   | 0.18µm              | 0.18µm            | 0.18µm      |

| Multipliers/ROMs                            | 1/0              | 0.256             | 0.0               | 00                  | 00                | W           |

| Adders                                      | 26               | 16                | 92                | 12+18ALU*+16SAT     | 50+16AT           | 46+16 ECAT* |

| DA-precision                                |                  |                   | 12 bits           | 13 bits             | 13 bits           | 9 bits      |

| Throughput Rate (pels/sec)                  | 100 M            | 100 M             | 77 M <sup>1</sup> | 250 M               | 400 M             | 16          |

| Gate Counts (NAND2) <sup>‡</sup>            | 60 K             | 25.5 K            | 22.5 K            | 27.8 K              | 39.8 K            | 22.2 K      |

| Hardware Efficiency                         | 1.6              | 3.92              | 3.42              | 9                   | 10.05             | 45          |

| Accuracy<br>(CCITT <sup>©</sup> Compatible) | Yes              | Yes               | Yes               | NA                  | NA                | Yes         |

\* ALU: Arithmetic logic unit. 4 transistors per NAND2 gate for different technology. CCITT: Consultative Committee for International Telegraph and Telephone.

Fig. 3. Architecture of the proposed 1-D 8-point DCT

Fig.4. Core layout and characteristics

accuracy with more area overhead. The proposed DCT core uses low-error ECAT to achieve a high-speed design, and the DA-precision can be chosen as 9 bits to meet the PSNR requirements for reducing hardware costs. The proposed DCT core has the highest hardware efficiency, defined as follows (based on the accuracy required by the presented standards)

Hardwar  $\notin$  fficienc (10³ pels/s)=  $\frac{\text{Throughpu} \Re \text{ate}}{\text{GateCounts}}$ . (23)

TABLE III 9-BIT DA-BASED COEFFICIENT MATRIX ee C

| FPGA-Chip              | 2     | C2VP | 30       | XC3S200 |          |

|------------------------|-------|------|----------|---------|----------|

| Architecture           | [15]  | [16] | Proposed | [17]    | Proposed |

| # of 4 input LUTs      | 10310 | 2618 | 2990     | 2271    | 2847     |

| # of Slices            | 5729  | 2823 | 1872     | 1221    | 1585     |

| # of Slices Flip Flops | 3736  | 3431 | 1837     | 616     | 1817     |

| Clock Freq. (MHz)      | 149   | 107  | 99       | 50      | 61       |

| Throughput (M-pels/s)  | 149   | 107  | 792      | 400     | 488      |

| Power (mW)             | N/A   | N/A  | 166.8    | 281     | 91       |

Furthermore, the proposed 2-D DCT core synthesized by using Xilinx ISE 9.1, and the Xilinx XC2VP30 FPGA can achieve 792 mega pixels per second (Mpels/sec) throughput rate (up to about 7 folds of previous work . Table V compares the proposed 2-D DCT core with previous FPGA implementations.

$<sup>\</sup>bigstar$  ECAT: The proposed error-compensated adder-tree. 77 MHz 1 GHz , where denominator 13 is the number of shifting and addition computation cycles.

#### **CONCLUSION**

In this brief, a high-speed and low-error 8 8 2-D DCT design with ECAT is proposed to improve the throughput rate significantly up to about 13 folds at high compression rates by operating the shifting and addition in parallel. Furthermore, the proposed errorcompensated circuit alleviates the truncation error in ECAT. In this way, the DA-precision can be chosen as 9 bits instead of 12 bits so as to meet the PSNR requirements. Thus, the proposed DCT core has the highest hardware ef-ficiency than those in previous works for the same PSNR requirements. Finally, an area-efficient 2-D DCT core is implemented using a TSMC 0.18-µ m process, and the maximum throughput rate is 1 Gpels/s. In summary, the proposed architecture is suitable for high compression rate applications in VLSI designs.

#### REFERENCES

- Y. Wang, J. Ostermann, and Y. Zhang, Video Processing and Communications, 1st ed. Englewood Cliffs, NJ: Prentice-Hall, 2002.

- [2] [2] Y. Chang and C. Wang, "New systolic array implementation of the 2-D discrete cosine transform and its inverse," *IEEE Trans. Circuits Syst. Video Technol.*, vol. 5, no. 2, pp. 150–157, Apr. 1995.

- [3] C. T. Lin, Y. C. Yu, and L. D. Van, "Cost-effective triple-mode reconfigurable pipeline FFT/IFFT/2-D DCT processor," *IEEE Trans. Very Large Scale Integr. Syst.*, vol. 16, no. 8, pp. 1058–1071, Aug. 2008.

- [4] S. Uramoto, Y. Inoue, A. Takabatake, J. Takeda, Y. Yamashita, H. Yerane, and M. Yoshimoto, "A 100-MHz 2-D discrete cosine transform core processor," *IEEE J. Solid-State Circuits*, vol. 27, no. 4, pp. 492–499, Apr. 1992.

- [5] S. Yu and E. E. S., Jr., "DCT implementation with distributed arithmetic," *IEEE Trans. Comput.*, vol. 50, no. 9, pp. 985–991, Sep. 2001.

- [6] P. K. Meher, "Unified systolic-like architecture for DCT and DST using distributed arithmetic," *IEEE Trans. Circuits Syst. I, Reg.Papers*, vol. 53, no. 12, pp. 2656–2663, Dec. 2006.

- [7] A. M. Shams, A. Chidanandan, W. Pan, and M. A. Bayoumi, "NEDA: A low-power high-performance DCT architecture," *IEEE Trans. Signal Process.*, vol. 54, no. 3, pp. 955–964, Mar. 2006.

- [8] M. R. M. Rizk and M. Ammar, "Low power small area high performance 2D -DCT architecture," in *Proc. Int. Design Test Workshop*, 2007, pp.120–125.

- [9] Y. Chen, X. Cao, Q. Xie, and C. Peng, "An area efficient high performance DCT distributed architecture for video compression," in *Proc. Int. Conf. Adv. Comm. Technol.*, 2007, pp. 238–241.

- [10] C. Peng, X. Cao, D. Yu, and X. Zhang, "A 250 MHz optimized distributed architecture of 2D 8 × 8 DCT," in *Proc. Int. Conf. ASIC*, 2007, pp. 189–192.

- [11] C. Y. Huang, L. F. Chen, and Y. K. Lai, "A high-speed 2-D transform architecture with unique kernel for multi-standard video applications," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2008, pp. 21–24.

- [12] S.S. Kidambi, F. E. Guibaly, and A. Antonious, "Area-efficient multipliers for digital signal processing applications," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 43, no. 2, pp. 90–95, Feb. 1996.

- [13] K. J. Cho, K. C. Lee, J. G. Chung, and K. K. Parhi, "Design of low-error fixed-width modified booth multiplier," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 12, no. 5, pp. 522–531, May 2004.

- [14] L. D. Van and C. C. Yang, "Generalized low-error areaefficient fixed-width multipliers," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 8, pp. 1608–1619, Aug. 2005.

- [15] C. C. Sun, P. Donner, and J. Gotze, "Low-complexity multipurpose IP core for quantized discrete cosine and integer transform," in *Proc. IEEE Int. Symp. Circuits Syst.*, 2009, pp. 3014–3017.

- [16] A. Tumeo, M. Monchiero, G. Palermo, F. Ferrandi, and D. Sciuto, "A pipelined fast 2D-DCT accelerator for FPGA-based SoCs," in *Proc. IEEE Comput. Soc. Annu. Symp. VLSI*, 2007, pp. 331–336.

- [17] S. Ghosh, S. Venigalla, and M. Bayoumi, "Design and implementation of a 2D-DCT architecture using coefficient distributed arithmetic," in *Proc. IEEE Comput. Soc. Ann.* Symp. VLSI, 2005, pp. 162–166.

#### GAIT RECOGNITION USING ANGLE AND FUZZY LOGIC

#### <sup>1</sup>AKHILESH SINGH & <sup>2</sup>JYOTI BHARTI

1,2Computer Science & Engineering, M A N I T, Bhopal, India Information Technology, M A N I T, Bhopal, India

**Abstract**—this paper introduces a new gait recognition approach using angle computation and fuzzy logic. We proposed a gait system with the help of fuzzy inference system (FIS) for better gait recognition rate. This approach is tested on a database of video sequences, corresponding 17 people. The previous approaches of gait recognition are compared with our proposed method. We get better recognition rate as compared to previous methods. Our method is based on dynamic body parameters. We have taken two component of human body. The first component is hand and second component is feet. The second component is subdivided into two parts i.e. toe and heel of both right and left leg. Our proposed method increase the matching accuracy which is lies between 75 to 86 percent.

**Keywords**- Gait recognition, angle, fuzzylogic, FIS(fuzzy inference system), biometric.

#### I. INTRODUCTION

In the present world scenario, the importance of application requiring human identification, security measures has increased drastically and is ever growing. In response to this demand new technologies are being developed to achieve requisite level of security. One of these technologies is referred to as biometrics biometrics refers to the automatic recognition of a person based on their physiological or behavioral characteristics. Physical and behavioral characteristics of each and every people are different and non transferable Human gait is an important and promising biometric resource for identification. Gait recognition is classified in to two methods namely model based and model free. In this paper we use Fuzzy inference system to achieve better gait recognition rate.

A new application of computer vision dealing with the analysis of images involving humans. There has been keen interest in human movement from a wide variety of disciplines [3].A literature including medical and physiological studies, indicating the potential of gait in personal identification, in psychology, a vast studies on human perception by Johansson [2]. each biometrics has its pros and cons, and the choice depends on the application. No single biometric is expected to effectively meet the aspects of all the application, a specific biometric is choose for an application by matching the properties of biometric and the operational mode of the application.[1][12]. Biometric system is basically a pattern recognition system that operates by a collecting data from an individual, extracting a feature set from the collected data, and comparing this feature set against the template set in the database. Biometricsare face, fingerprint, DNA, iris and retinal patterns, voice, hand geometry, gait, ear and signature. Gait is the best biometric for human recognition. We create gait recognition system with the help of fuzzy inference system in our proposed method.

This paper is organized as follows. Section II Summaries some related existing methods for human gait recognition. Gait, fuzzylogic, fuzzy inference system and its methods and functions is described in section III.Section IV provides our proposed method. Experimental results & analysis are presented in section V, followed by Conclusions & future scope in Section VI.

#### II. RELATED WORK

A survey of the current analysis of human movement has been outlined by Gavrilla[3]. he surveyed the work on visual analysis looking at gestures and whole body movement and outlined ability to recognize people and their activities by computer. According to Garvilla[3] survey the visual analysis of human movement has become a major application in world of computer vision. An effective gait recognition approach based GEI (gait Energy image)was proposed by [X.Yang, Y.Zhang, T.Zhang, E.Gheng&J.Yang[5]] Existing methods for gait recognition can be classified in two categories first is model based and 2<sup>nd</sup> is motionbased. Among the motion based ones, there is an effective method using Gait energy image as gait representation.GEI is the average silhouette over one gait cycle.

Human gait is a promising biometrics resource. [Xuelong Li. Stephen J. Maybank, Shuicheng Yan, Dacheng Tao, Dong Xu [7]] had studied gait components and their application to gender recognition. In their research, the information about gait was obtained from the motions of different parts of the silhouette. human silhouette was segmented in to seven components namely head ,arm,trunk,thigh, front leg, back leg and feet .this paper helped me a lot to write this paper, In my paper I have considered only five parts of the body namely hand, right heel, right toe, left heel and left toe.

[Joao P .Ferreira , Manuel Crisostomo, A. Paulo Coimbra, David Carnide , Antonio Marto [8]] did the

tracking and analysis of the human motion, specially the Gait, by using computational vision there's aim to obtain gait signatures using computer vision techniques and to extract kinematics features for describing motion of human, to obtain this, white LED placed on several points on an individual's body partsand guided by automatic knowledge, gait properties were extracted.

This study goes some way towards the research work done by different researchers in the field of biometric resource gait. I have gone through the research work of different researchers that are dealt in study of gait.

#### III. GAIT AND FUZZY LOGIC

The definition of Gait is defined as "A peculiar way or manner one walks" and is a complex spatiotemporal biometrics. The walking style of every person is unique. Due to this it is sufficiently used for verification in security applications. Using gait as a biometric is a relatively new area of study .In computer vision recognizing humans by gait has recently been investigated. Human gait may be defined as a means of identifying individuals by the way they walk [10]

When we compared gait to other biometrics, gait has some unique characteristics. The most attractive feature of gait as a biometrics is its unobtrusiveness. It means, unlike other biometrics, it can be captured at a distance without physical contacts of the observed subject. Most other biometrics such as fingerprints, hand geometry, voice, face and signature can be captured only by physical contact or at a close distance from the recording instrument. Gait also has the advantage of being difficult to steal, hide or fake [13]

There are some limitations in gait capturing that make it difficult to identify and record all parameters that affect gait .it is affected by clothes, footwear, walking speed, and emotional condition etc.

Fuzzy logic is a mathematical approach to solving problems. It excels in producing exact result from imprecise data and is especially useful in computer and electronics application. In classical logic, an object takes on a value of either 0 or 1 .In fuzzy logic, a statement can assume any real value between 0 and 1, representing the degree to which an element belong to given set. Fuzzy set is defined as a set whose elements have degree of membership.

- A fuzzy subset F of a set S can be defined as a set of ordered pairs. The first element of the ordered pair is from the set S, and the 2<sup>nd</sup> element from the ordered pair is from the interval [0, 1].

- The value zero is used to represent non membership; the value one is used to represent complete membership and the value in between are used to represent degrees of membership.

The common method of representing Fuzzy set is

$$A = \{x, \mu_A(x)\} \times \varepsilon X \qquad (1)$$

Where x is an element in X and  $\mu_A(x)$  is the membership function of set A which defines the membership of fuzzy set A in the universe of discourse, X. [23]

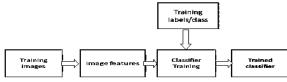

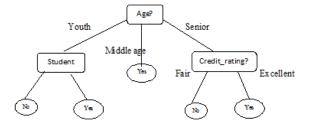

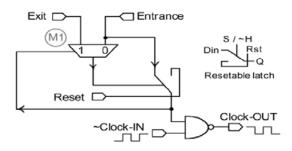

A. Fuzzy inference system

Fuzzy inference system is a process of formulating the mapping from a given input to an output using fuzzy logic. The mapping then provides a basis from which decision can be made or pattern discerned. the process of fuzzy inference involves all the process i.e. Membership function, logical operations, fuzzification , defuzzification and if —then rules. Fuzzy inference systems have been applied successfully in fields such as automatic control, data classification, decision analysis, expert system and computer vision.[23]

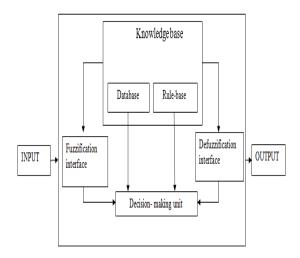

Basically, fuzzy inference system consists of five functional blocks as shown in Figure III.1

- A rule base containing a number of fuzzy if

-then rules;

- A database which defines the membership functions of fuzzy sets used in the fuzzy rules:

- A decision making unit which perform inference operation on the rules.

- A fuzzificationinterface which transforms the crisp inputs in to degree of match with liguistic values;

A **defuzzification interface** which transform the fuzzy results on the interface in to a crisp output

Figure III.1 Fuzzy inference system

#### Steps performed by Fuzzy inference system are:

- 1. Compare the input variables with the membership functions on the premise part to obtain the membership values of each linguistic label.

- 2. Combine the membership values on the premise part to get weight of each rule.

- **3.** Generate the qualified consequent of each rule depending on the firing strength.

Aggregate the qualified consequents to produce a crisp output.

#### B. Fuzzy membership functions

#### • Triangular membership function

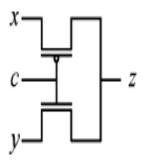

It is a special case of linear representation. Triangular membership function is represented by a triplet notation  $x \square \square < a,b,c>$ -triangular membership function is defined as :

$$\mu_{A}(x) = \begin{cases} 0, \text{for } x < a \\ \frac{x-a}{b-a}, \text{ for } a \le x \le b \\ \frac{c-x}{c-b}, \text{ for } b \le x \le c \\ 0, \text{ for } x > c \end{cases}$$

#### • Trapezoidalfunctions

It is defined by four parameters, x <a,b,c,d>. A trapezoidalfunction formally described by

$$\mu_{A}(x) = \begin{cases} 0, \text{ for } x < a \\ \frac{x-a}{b-a}, \text{ for } a \le x \le bv \end{cases}$$

$$1, \text{ for } b \le x \le c \dots (3)$$

$$\frac{d-x}{d-c}, \text{ for } c \le x \le d$$

#### Normalized Gaussian functions

It is another fuzzy membership function that isoften used to represent vague, linguistic terms is the Gaussian which is defined by two parameters

$x < \sigma, c >$ , is represented by :

$$\mu_{A}(x) = e^{-(x-c)^{2}} / 2\sigma^{2}$$

(4)

#### C. Mamdani Fuzzy models

Mamdani's fuzzy inference method is the most commonly seen fuzzy methodolgy.it was among the first control system built using fuzzy set theory. it was proposed in 1975 by Ebrahim Mamdani.mamdani type inference, expects the output membership functions to be fuzzy sets. after the aggregation process, there is a fuzzy set for each output variable that needs defuzzification.it is possible, and in many cases much more efficient

To use a single spike as the output membership functions rather than a distributed fuzzy set .this type of output known as singleton output membership function and it can be thought as a predefuzzified fuzzy set. it enhance the efficiency of the defuzzification process because it greatly simplifies the computation required by the more general Mamdani method, which finds the centroid of a two dimensional function.[23]..it is well suited to human input and it is intutive due to this property it is more advantageous than sugeno method.

#### D. Sugeno Fuzzy models

it is also known as Takagi Sugeno- Kang, Method of fuzzy inference. introdued in 1985, it is similar to mamdani method to many respects. The first two parts of fuzzy inference process, fuzzyfying the inputs and applying the fuzzy operator, are exactly the same. the main difference between Mamdani and Sugeno is that the Sugeno output membership function are either linear or constant.it is computationally efficient and it works well with linear technique

A typical rule in a sugeno model has the form if input 1 = x and input 2 = y, then output is z = ax+by+c,

"if x is A & y is B then z = f(x,y)"

where A & B are fuzzy sets in the antecedent, while z = f(x,y) is a crisp function in the consequent

- if f(x,y) is a first order polynomial, then the resulting fuzzy inference is called a first order Sugeno fuzzy model.

- if f(x,y) is a constant then it is a zero order Sugeno fuzzy model(special case of Mamdani model) for a zero order Sugeno model, output level z is a constant (a=b=0).

#### IV. PROPOSED METHOD

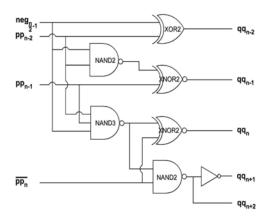

In our proposed method we have taken two components of human body first component is hand and another component is leg.2<sup>nd</sup> component is subdivided into toe and heel of both left and right feet. We insert a white dot point on component selected parameters at all frames as shown in figure IV.1 below.

Figure IV.1 White dot points on subject selected parameters

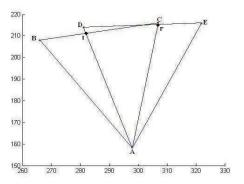

Thesewhite dotted frames of each individual inputted in our gait system, which is designed in MATLAB for gait recognition. Two triangles are created between above features. First triangle is drawn between hand and two heels of both feet (right heel and left heel) and 2<sup>nd</sup> triangle is created between same hand and two toe of both feet (right toe and left toe).we find two intersecting points between these two triangles and angles at these intersecting points lies between 0 to 180 degrees shown in figure IV.2 below:

Figure IV.2 I and I' are intersecting points betweenΔ's ABC &

I' & I are two intersecting points which have to be computed using parametric line equation and angles at these intersecting points [22].here point A represent Hand and point B,C represents toe of both feet(left and right),point D,C represents heel of both feet(Left and Right) shown in figure IV.2 after that we compute mean values of two angles of an individual subject. After computation of mean values of two angles we take these values as input of our fuzzy inference system .FIS compare these values with the database values and after that FIS produces result according to the fuzzy rule as follows:

- if (Angle 1 is Yes) and (Angle 2 is Yes) Then (match is Excellent) (1)

- if (Angle 1 is No) and (Angle 2 is Yes) Then (match is Average) (1)

- if (Angle 1 is Yes) and (Angle 2 is No) Then (match is Average) (1)

- if (Angle 1 is No) and (Angle 2 is No) Then (match is No match) (1)

- if (Angle 1 is No) and (Angle 2 is No) Then (match is No match) (0)

- if (Angle 1 is Yes) and (Angle 2 is Yes) Then (match is excellent) (0)

- if (Angle 1 is No) and (Angle 2 is Yes) Then (match is Average) (0)

- if (Angle 1 is Yes) and (Angle 2 is No) Then (match is Average) (0)

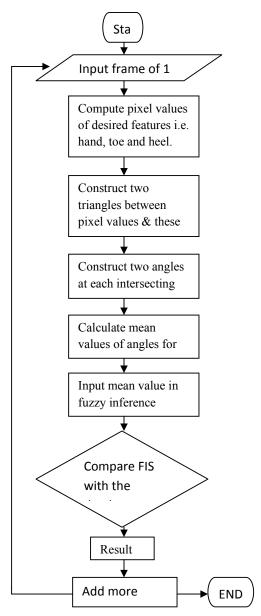

#### A. Proposed Algorithm

The Algorithm is designed for gait recognition using mean value of angles and fuzzy logic .fuzzy logic improves our recognition rate and matching accuracy.

- 1) start

- 2) input subjects frames

- 3) Convert frames into grayscale.

- 4) compute pixel values of desired features i.e.

- Arm

- Right toe and heel

- left toe and heel..

- 5) construct two triangle between pixel values of these desired features.

- 6) compute two angles at each intersecting points.

- 7) find mean value of two angles.

- 8) input mean values of angles in a fuzzy inference system(FIS).

- 9) compare FIS(Fuzzy inference system) with the database values.

- 10) FIS produce results.

- 11) store result in database.

- 12) Repeat step 1 to 11 for another subject.

- 13) End

#### B. Proposed flow chart

Figure IV.3 Flowchart showing Proposed Gait System

#### V. EXPERIMENTAL RESULT & ANALYSIS

Our experiments are done on CASIA dataset A[15] for analysis of gait recognition of proposed method. We have taken 17 subjects for gait recognition analysis. We have done gait analysis on gray level images. When we input dotted RGB frames of an individual subjects in our gait system after that these RGB frames are converted in to gray scale for further processing. Only two parameters we have considered out of seven components of human body [7]. Parametric line equation provides better variation in each subject.

Table V.1 shows the results of mean value angles of two angles that we calculated between two triangles intersecting points, created using parametric line equation.

| Subjects | Angle 1st mean values | Angle 2 <sup>nd</sup> mean<br>values |

|----------|-----------------------|--------------------------------------|

| A        | 75.064                | 86.655                               |

| В        | 78.3647               | 94.0671                              |

| C        | 77.0836               | 97.8904                              |

| D        | 80.5067               | 93.0817                              |

| E        | 82.452                | 99.2792                              |

| F        | 86.109                | 103.0987                             |

| G        | 89.2465               | 101.7519                             |

| Н        | 84.6639               | 103.2414                             |

| I        | 81.4461               | 97.137                               |

| J        | 82.5426               | 96.7582                              |

| K        | 72.0027               | 81.1398                              |

| L        | 87.3647               | 102.2194                             |

| M        | 84.767                | 104.8248                             |

| N        | 79.9892               | 89.244                               |

| O        | 75.4974               | 86.4331                              |

| P        | 80.7623               | 92.0858                              |

| Q        | 82.3511               | 98.7227                              |

|          |                       |                                      |

Table V.1 Experimental result of first and secondangle mean value of individual subjects

Table V.2 shows that we compare the result with fuzzy logic and without fuzzy logic .the matching accuracy increases with fuzzy logic .

|          | Without Fu                              | ızzy Logic                                 |                     |        |

|----------|-----------------------------------------|--------------------------------------------|---------------------|--------|

| Subjects | Angle 1 <sup>st</sup><br>mean<br>values | Angle<br>2 <sup>nd</sup><br>mean<br>values | With Fuzzy<br>Logic | Values |

|          | 75.064                                  | 86.655                                     |                     | 80.043 |

| Α        | 78.3647                                 | 94.067                                     | Good                | 86.537 |

| В        | 77.0836                                 | 97.890                                     | Excellent           | 83.278 |

| С        | 80.5067                                 | 93.081                                     | Good                | 84.269 |

| D        | 82.452                                  | 99.279                                     | Good                | 81.431 |

| E        | 86.109                                  | 103.09                                     | Good                | 86.536 |

| F        | 89.2465                                 | 101.75                                     | Excellent           | 79.440 |

| G        | 84.6639                                 | 103.24                                     | Good                | 77.241 |

| Н        | 81.4461                                 | 97.13                                      | Good                | 86.537 |

| 1        | 82.5426                                 | 96.75                                      | Excellent           | 86.758 |

| J        | 72.0027                                 | 81.13                                      | Excellent           | 76.139 |

| K        | 87.3647                                 | 102.21                                     | Good                | 83.657 |

| L        | 84.767                                  | 104.82                                     | Good                | 82.824 |

| M        | 79.9892                                 | 89.24                                      | Good                | 75.104 |

| N        | 75.4974                                 | 86.433                                     | Average             | 80.433 |

| 0        | 80.7623                                 | 92.085                                     | Good                | 77.751 |

| Р        | 82.3511                                 | 98.722                                     | Good                | 81.402 |

| Q        |                                         |                                            | Good                |        |

Table V.2 Experimental result of first and second angle mean value of individual subjects using Fuzzy inference system

Result shown in table V.2 depicts that the mean values of two angles take as an input of fuzzy inference system then fuzzy inference system and it compare with the database the above results shows

that " matching accuracy lies between 75 to 86 percent".

#### Comparison with other Algorithm

| Algorithm                                                                    | CCR               |

|------------------------------------------------------------------------------|-------------------|

| Static body Parameters (Georgia Tech)                                        | 73%(18)           |

| Motion based Eigen space analysis(UMD)                                       | 75%(44)           |

| Method based on Positioning body joints                                      | 78%(118)          |

| Method based on dynamic body<br>Parameters                                   | 78%(17)           |

| Proposed method based on dynamic body parameters with fuzzy inference system | 75% to<br>86%(17) |

### Table V.3 Experimental results compared with other Algorithm

From Table V.3 it can be seen that higher recognition rate has been obtained according to gait recognition method based on the proposed Algorithm.

#### CONCLUSIONS AND FUTURE SCOPE

In this paper, we have shown a new approach to enhance gait recognition rate with fuzzy logic. It is clear from our experiments that the assumptions made on dynamic features of human body (i.e. hand and feet) increase gait recognition and the average classification. We have used fuzzy logic on mean values of two angles. Due to this, matching accuracy is increases and it lies between 75 to 86 percent. We have done our experiment on CASIA dataset A of 17 subjects. Our result analysis on this dataset gives better recognition rate. our experiment result shows that the concept of fuzzy logic with mean values of both angles gives better gait recognition.

The present study was occurred on the side view of subject gait similar study can be conducted on different view angle of subject gait. Our study was confined to a sample of 17 subjects of CASIA dataset. Similar work can be conducted on more sample database of different organization for result analysis.

#### REFERENCES

- Anil. K.Jain, Arun Ross, Salil Prabhakar: "An introduction to biometric recognition", IEEE Transactions on circuits and systems for

- video

- technology, vol. 14, no. 1,pp 67-80, January 2004.[2]. G.Johnsson:" Visual perception of biological motion and a modelfor its

- Analysis, Perception Psychophys". *IEEE conference on intelligent control and automa*, vol.14 (2), 201-211, 1973.

- [3]. D.M.Gavrila:" The visual analysis of human movement: a survey,

- Computer Vision and Image Understanding", *IEEE journal on intelligent systems*, vol. 73, no. 1, pp. 82-98, January 1999.

- [4] M.Patmurray, A.Bernard Drought, Ross. C.Kory: "Walking pattern of normal men", IEEE Journal on pattern analysis and machine, vol. 46.335-360.1964.

- [5].X.Yang, Y.Zhou, T.Zhang, J.Yang: "Gabor phase based gait recognition,

- Electronics Letters ", *IEEE Journal on pattern analysis and machine*, Vol. 44 No. 10,8th May 2008.

- [6]. Khalid Bashir, Tao Xiang, Shaogang Gong: "Feature selection on gait energy image forhumanidentification" IEEE International

- energy image forhumanidentification",IEEE International Conference on Acoustics, Speech, and Signal Processing ,pp 44-50,2008

- 7]. Xuelong Li, Stephen J. Maybank, Shuicheng Yan, Dacheng Tao, and Dong Xu,."Gait Components and Their Application to Gender Recognition", IEEE Transactions on Systems, Man, and Cybernetics Part C Applications and Reviews, vol. 38, no. 2,

- March 2008.

[8].Joao P. Ferreira, Manuel Crisostomo, A. Paulo Coimbra, David Carnide, and Antonio Marto: "A Human Gait Analyzer", IEEE international symposium on intelligent signal processing, October 2007

- [9]. Ryuhei Okuno, Satoshi Fujimoto, Jun Akazawa, Masaru Yokoe.

- Saburo Sakoda and Kenzo Akazawa:"Analysis of spatial temporal

- plantar pressure pattern during gaitin Parkinson's disease", 30th

- Annual International IEEE EMBS Conference Vancouver, British

- Columbia, Canada, 20-24, pp, 24-27, August 2008.

- [10]. Jang-Hee Yoo, Mark S. Nixon and Chris. J. Harris: "Extracting Human Gait Signatures by Body Segment Properties", Fifth IEEE

- Southwest

Symposium on Image Analysis and Interpretation, 0-7695-

- Symposium on Image Analysis and Interpretation, 0-/695-1537-1/02, 2002.

- [11] James R. Gage, Peter A. Deluca , Thomas S. Renshaw: "Gait Analysis Principles and Applications", The Journal of bone and joint surgery, vol. 77, 1607-1623, 1995.

- [12]. Anil K. Jain, Arun Ross, and Sharath Pankanti: "Biometrics: A Tool for Information Security", IEEE Transactions on Information

- Forensics and Security, vol. 1, no. 2,pp 21-38, June 2006.

- [13].Nikolaos V. Boulgouris, Dimitrios Hatzinakos, and Konstantinos

- N. Plataniotis: "A challenging signal processing technology for biometric identification", *IEEE Signal Processing Magazine*, pp 56-70,November 2005.

- [14]. Shiqi Yu, Tieniu Tan, Kaiqi Huang, Kui Jia and Xinyu Wu:" A Study on

- Gaitbased Gender Classification", *IEEE transaction on image processing*, vol.18, pp 52-64, august 2009.

- [15]. Center for Biometrics and Security Research (CBSR), www. Sinobiometrics.com

- [16]. www.orthoteers.com/gait.html.

- [17]. sprojects.mmi.mcgill.ca/gait/normal/intro.asp.

- [18]. Massimo Tistarelli, Stan Z.Li, Rama Chellappa: Handbook of Remote

- Biometrics for Surveillance and security.

- [19]. www.mathsworks.com.

- [20]. MATLAB and Its Applications in Engineering by Raj Kumar Bansal,

- Ashok Kumar Goel and Manoj Kumar Sharma.

- [21]. Gait Recognition: final report by Mark Ruane Dawson, Imperial College of Science, Technology and Medicine, London.

- [22]. http://workshop.evolutionzone.com/2007/09/10/code-2d-line-intersect/

- [23]. Neuro Fuzzy Systems by Lamba, V.K.First Edition,2008

## MATHEMATICAL MODEL OF INFORMATION AND A NEW APPROACH OF CODING IN IT

<sup>1</sup>S. K. PARHI & <sup>2</sup>L. DAS

<sup>1</sup>Vijayanjali Institute of Technology, Khantapada, Balasore-756043 <sup>2</sup>Delhi Technological University, New Delhi-110042

**Abstract**:- In this paper we are discussed about logical sentence coding for distinct messages by binary alphabets {0, 1}. The information model contains alphabets, words, sentences and messages are available in the practical purpose. The information and its relation discussed for clarification.

Keywards: - Logical Information, Partial Sum.

#### I. INTRODUCTION

In our discussion of the paper is that alphabet is the binary alphabet {0,1}. A code is also collection of logical sentence that are used to be represent distinct messages .A sentence in a code is also called a *code-sentence*. Suppose a logical sentence is transmitted from its source of information to its destination. In case of transmission, *inferences* such as noises might cause some of the 1's in the code-sentence to be received as 0's and some of the 0's to be received as 1's. There fore received sentence might no longer supposed as the transmitted one and that one is our aim to recover that transmitted sentence if at every case of possible.

Generally, in telephone wires strung between poles ,later the were cables on poles and in trenches .Next come microwave between relay towers on hill tops follow the were less communication system. Subsequently joined by microwave beam to and from satellites and fix points high wave equator. Now more and more long lines are *fiber-optic* cables. The microwave towers are spaced at 26 mile intervals in long chains that join cities. They are followed the *logical communication system* (LCS).

#### II. LOGICAL INFORMATION CODING

In modern communication system ,data items are constantly being transmitted from point to point .The basic unit of information called a message, is a finite sequence of character that we want to transmit is now represented as a sequence of melements from A .Choose our alphabet set  $A = \{0,1\}.Let\ A^m$  denote the binary sequence of length n. Let  $\widehat{+}$  be a binary operation on A such that for x and y in A. Then x  $\widehat{+}$  y is called partial sum of sequence length n means carry part is neglected during addition and one if both are different. For example

X=10101 and y=10011 then  $x + \hat{y}$  is 00110 To show that  $(A^m, +)$  is a group by using the properties. Let x be a sentence in A. We define the weight of x denoted by  $\omega(x)$  to be the number of 1's in x. The weight of 00110 is two. We define the weight of x and y denoted by  $\omega(x,y)$  to be the weight of x is  $\omega(x,y)$ . Note that the *partial sum* of two words is exactly carry part is neglected during sum and one if both are different . We establish a theorem as follows.

#### THEOREM:-2.1.

Let x,y and z be elements of  $A^m$ . Then

- (a)  $\omega(x,y) = \omega(y,x)$ .

- (b)  $\omega(x,y) \ge 0$ .

- (c)  $\omega(x,y) = 0$  if and only if x=y.

- (d)  $\omega(x,y) \le \omega(x,z) + \omega(z,y)$ .

**PROOF:-** The first three properties are simple to prove are not needed.

(d). For

$$x,y$$

in  $A^m$ ,  $|x + y| \le |x| + |y|$

If  $x \in A^m$ , then  $x + x = \overline{0}$ , the identity element in  $A^m$ .

Then

$$\omega(x,y)=|x + y|=|x + \bar{o} + y|$$

$=|x + \bar{c} + \bar{c} + y|$

$\leq |x + \bar{c} +$

Thus this establishes the theorem.

The transmission of information is to reduce the likelihood of receiving a sentence that differs from the sentence that was sent, the code sentence by means of a transmission channel. Then each code sentence  $x{=}e(a)$  is received as the sentence in  $A^m$ . This is received from each  $a\in A^m.$  e is a function and a may be identified. The noiseless or noiseful arises during transmission.

## III. MATHEMATICAL MODEL OF INFORMATION

As we observed that the information can be represented in either symbols , wards ,sentences and message form .The common syntax of representing any information is a mathematical expression .The different models are available in t-he practical purpose .We suggest a triplet  $(\Sigma, \delta, 0)$  for this purpose.

The symbols  $\Sigma$ ,  $\delta$  and 0 are used for the representation of a set of characters, transactions or relationship from any subset of  $\Sigma^*$  to  $\Sigma^*$  (set of all regular expressions defined on  $\Sigma$ ) and the set of operations (logical, arithmetical etc) the following proposition assures the encoding of information with this formulation .

#### PROPOSITION:-3.1

The set of all alphabets ,words ,sentences and messages are contained in the system  $(\Sigma, \delta, 0)$ .

#### PROOF:-

Let the system (  $\Sigma$  ,  $\delta$  ,0 ) be denoted as S .where  $\Sigma$  is the set of alphabets,  $\delta$  the transactions and 0 is a specific operations on the set of alphabets ,Suppose 0 is the concatenation operation,  $\delta$  is the identity transformation ,then

a

$$0 \lambda = \lambda 0$$

a =a for a  $\in \Sigma$

To verify the set of words belongs to S ,the transaction functions are to be considered from any subset of  $\Sigma^*$  to  $\Sigma^*$  and the operation 0 is the concatenation operation.

To show the set of sentences and messages belongs to the system  $(\Sigma\,,\,\delta,0),$  the choices of  $\delta$  and 0 should be specific. In this case the operation 0 can be any logical operations such as NOT,AND,NAND,NOR and EOR ,Implication etc.[]

#### EXAMPLE:-3.2

The sentence "This white car is mine" belongs to the information system  $(\Sigma, \delta, 0)$ . In this case  $\Sigma$  is the set of all English characters including the blank character 'b' and the null characters "lambda" the transaction function  $\delta$  is a mapping from subset of  $\Sigma^*$  to  $\Sigma^*$  such that  $\delta$ (this white car is mine)= thiswhitecarismine. This string is a word in  $\Sigma^*$ .

If  $T = \{b,a,c,e,h,I,m,n,r,s,t,w\}$ ,  $\delta: T \rightarrow \Sigma^*$  then for  $u \in \Sigma^*$  such that  $u = \{t,th,thi,this,thisb,thisbw,thisbwh,thisbwhite,thisbwhiteb,thisbwhitebc,thisbwhitebca,thisbwhitebcar.....}$

So 0 is the recursively concatenation operation.

#### IV. MESSAGE REPRESENTATION

Usually message are represented either in the sequential coding or in the alpha numeric forms. The communication protocols use different types of coding as per the data transmission equipments infrastructures and the security to the data contents. Most of the communication systems use sequential coding. One of the data transmission permission is obtained from the receiver 's end within the STX(start of text)and ETX(end of text) commands most of the massages are transmitted through the proper code. In fact, the codes are binary characters. Telephone network, Cable television network and Computer network etc, use binary codes for the data transmission, Surface mail (i.e., News paper etc.) or postal messages are encoding in any other type of characters, not necessarily binary codes.

#### V. INFORMATION AND ITS RELATIONSHIP WITH MESSAGE

Message carry information. All information derived from any message are either correct or wrong. The information can be interpreted as the proposition or predicates. The sentence connectors and parsers can degenerate information from the basic literal associated with the message.

#### VI. CONCLUSION

This paper gives the details clarification of different messages during transmission. The transmission of information from point to point and its basic unit called message. The *Telephone network, Cable television network and Computer networks etc.* use binary codes during data transmission. The binary coding is used in this paper is easily implemented in the personal computer system. The messages are either correct or wrong is identified by the system.

#### REFERENCES

- [1] Parhi, S.K., "Study of Certain Mathematical Modeling and Algorithm in the Information Technology", Ph. D. Thesis of Utkal University, Bhubaneswar, 2002, Appendix-3.

- [2] Liu,C.L., Elements of Discrete Mathematics, Mc. Graw Hill Book Company, 1985 P.359-363.

# DESIGN AND SIMULATION OF A NEW 2-DIMENSIONAL TRANSFORM TECHNIQUE FOR SINUS ARRHYTHMIA PATIENT'S ELECTROCARDIOGRAM SIGNAL COMPRESSION

#### <sup>1</sup>PUSHPENDRA SINGH & <sup>2</sup>OM PRAKASH YADAV

<sup>1</sup>ME Scholar (Communication)

<sup>2</sup>Electronics and Telecommunication department

<sup>1,2</sup>Chhatrapati Shivaji Institute of Technology, Durg, INDIA

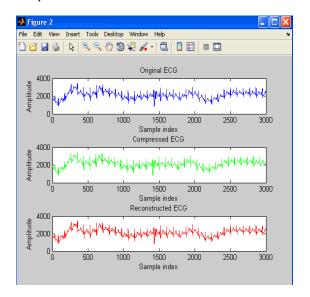

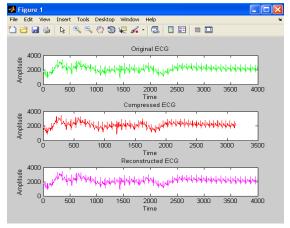

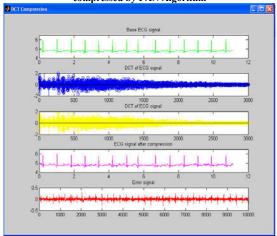

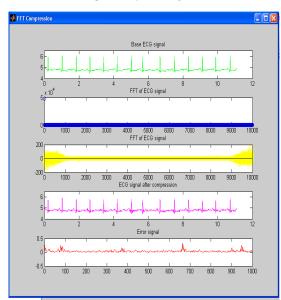

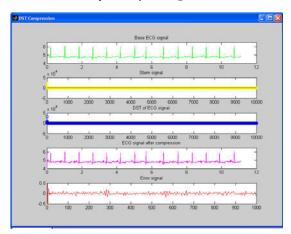

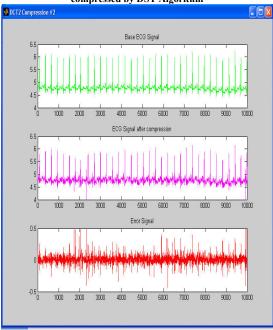

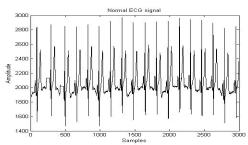

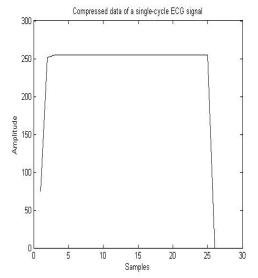

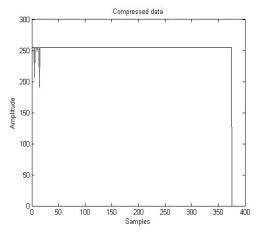

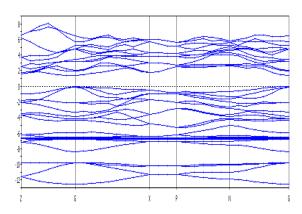

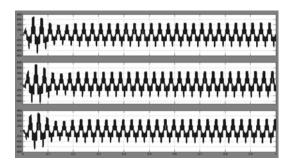

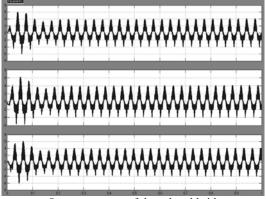

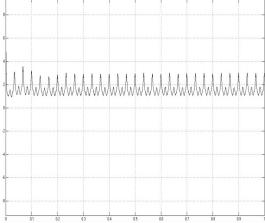

Abstract— Electrocardiogram signal compression algorithm is needed to reduce the amount of data to be transmitted, stored and analyzed, without losing the clinical information content. In this work takes the real time data of the Sinus Arrhythmia patient and investigates a set of ECG signal compression schemes to compare their performances in compressing Sinus Arrhythmia patient's ECG signals. These schemes are based on transform methods such as discrete cosine transform (DCT), fast Fourier transform (FFT), discrete sine transform (DST), and their improvements. An improvement of a discrete cosine transform (DCT)-based method for electrocardiogram (ECG) compression is also presented as DCT-II. A comparative study of performance of different transforms is made in terms of Compression Ratio (CR) and Percent root mean square difference (PRD). The appropriate use of a block based DCT associated to a uniform scalar dead zone quantiser and arithmetic coding show very good results, confirming that the proposed strategy exhibits competitive performances compared with the most popular compressors used for ECG compression. Each specific transform is applied to a pre-selected data segment from the CSE database, and then compression is performed.

**Keywords**— Compression Ratio, Compression factor, Compression time, ECG, PRD.

#### I. INTRODUCTION

An ECG signal is a graphical representation produced by an electrocardiograph, which records the electrical activity of the heart over time. The ambulatory monitoring system usually requires continuous 12 or 24-hours ambulatory recording for good diagnostic quality. For example, with the sampling rate of 360 Hz, 11 bit/sample data resolution,

a 24-h record requires about 43 MByte per channel. So, 12-channel system requires nearly 513.216 MByte of storage disks daily.

Because of the tremendous amount of ECG data generated each year, an effective data compression schemes for ECG signals are required in many practical applications including ECG data storage or transmission over telephone line or digital telecommunication network. ECG data compression techniques are typically classified into three major categories; namely direct data compression [3]-[4], transform coding [5]-[8], and parameter extraction methods [9]-[11]. The direct data compression methods attempt to reduce redundancy in the data sequence by examining a successive number of neighboring samples. These techniques generally eliminate samples that can be implied by examining preceding and succeeding samples. Even though many compression algorithms have been reported so far in the literature, not so many are currently used in monitoring systems and telemedicine.

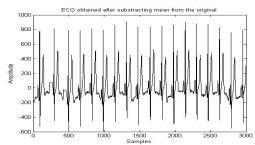

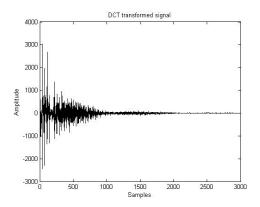

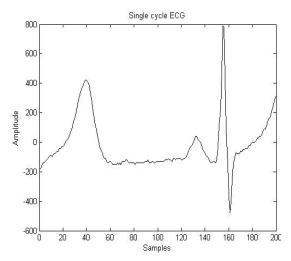

In this paper a new compression technique asked on transform coding-II and QRS complex estimation is proposed. There are two motivations in this work. The first motivation is the QRS complex estimation using the extraction of significant features of ECG waveform. The second motivation is the selection of the threshold levels in each sub band such that high CR and low PRD are obtained. The significant features of ECG waveform are extracted to estimate the QRS complex. Then, the estimated QRS-complex is subtracted from the original ECG signal. After that, the resulting error signal is discrete cosine transformed and the coefficients are threshold based on the energy packing efficiency. Finally the significant coefficients are coded and stored or transmitted.

### II. FEATURE EXTRACTION OF ECG SIGNAL

It has now gone beyond the capacity of the expert cardiologist to take care of large numbers of cardiac patients efficiently & effectively. Therefore, computer- aided feature extraction and analysis of ECG signal for disease diagnosis has become the necessity. The first step in computer aided diagnosis is the identification & extraction of the features of the ECG signal. The QRS complex is the most prominent feature and its accurate detection forms the basis of extraction of other features and parameters from the ECG signal. There are a number of methods, some of which deal with detection of ECG wave segments, namely P, QRS and T, while others deals with

detection of QRS complexes. A good amount of research work has been carried out during the last five decades for the accurate and reliable detection of QRS segment in the ECG signal. The QRS detection algorithms developed so far can be broadly placed into four categories: (i) Syntactic approach (ii) Non-Syntactic approach (iii) Hybrid approach and (iv) Transformative approach.

#### [A] Syntactic Approach:

The syntactic approach is basically pattern recognition based QRS detection techniques. The ECG signal is first reduced into a set of elementary patterns like peaks, durations, slopes, interwave segments and thereafter use rule based grammar. The signal is represented as a composite entity of peaks, duration, slopes and interwave segments. These patterns are then used to detect the QRS complexes in the ECG signal. These methods are time consuming and require inference grammar in each step of execution for QRS detection.

#### [B] Non-syntactic Approach:

Non-syntactic type is the most widely used class of ECG feature extraction techniques. In this class, we find the use of amplitude, slope and threshold limit as well as the use of different filters, mathematical functions and models. Okada reported a five step digital filter, which removes components other than those of QRS complex from the recorded ECG [24]. The final step of the filter produces a square wave and its on-intervals correspond to the segments with QRS complexes in the original signal.

#### [C] Hybrid Approach:

In hybrid approach, the syntactic and non-syntactic approaches are combined to detect the QRS complex. These are not in common use, as in syntactic approach, the trace is being made on actual morphology of the ECG signal and in non-syntactic approach; there is no consideration to maintain the morphology of the ECG signal.

#### [D] Transformative Approach:

Transformative Techniques, namely Fourier Transform, Cosine Transform, Pole –zero Transform, Differentiator Transform, Hilbert Transform and Wavelet Transform are being used for the QRS detection. The use of these transforms on ECG signal helps to characterize the signal into energy, slope, or spike spectra, and thereafter, the temporal locations are detected with the help of decision rules like thresholds of amplitude, slope or duration. Murthy and Prasad proposed a solution to the fundamental problem of ECG analysis, viz., delineation of the signal into its component waves [25].

#### III. COMPRESSION TECHNIQUES

Lossless compression algorithms: the Run Length Encoding Algorithm, Huffman Encoding Algorithm, Shannon Fano Algorithm, Lempel Zev Welch Algorithm, Discrete Cosine Transform, Fast Fourier Transform, Discrete Sine Transform and Discrete Cosine Transform-II are implemented and tested with a set of ECG signal. Performances of the compression methods are also evaluated at the end of the paper.

#### [A] Run Length Encoding

Run Length Encoding or simply RLE is the simplest of the data compression algorithms. The consecutive sequences of symbols are identified as runs and the others are identified as non runs in this algorithm. This Algorithm deals with some sort of redundancy [4]. It checks whether there are any repeating symbols or not, and is based on those redundancies and their lengths.

#### [B] Huffman fano Approach:

Huffman fano Algorithms calculate the frequencies first and then generate a common tree for both the compression and decompression processes [5]. Huffman Encoding and Shannon Fano approaches are implemented and executed independently.

#### [C] Discrete Cosine Transform (DCT):

A discrete cosine transform (DCT) [19] expresses a sequence of finitely many data points in terms of a sum of cosine functions oscillating at different frequencies [9]. Discrete Cosine Transform is a basis for many signal and image compression algorithms due to its high de-correlation and energy compaction property [10].

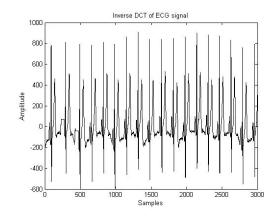

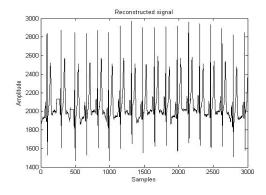

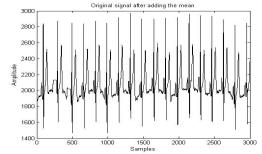

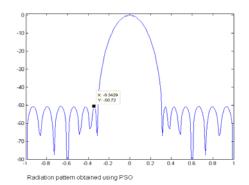

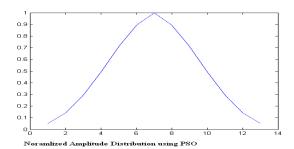

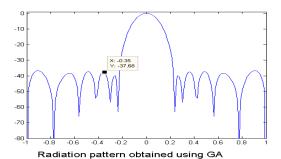

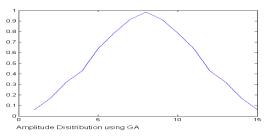

#### [D]Fast Fourier Transform (FFT):